начиная с какого процессора процессоры имеют встроенный сопроцессор с плавающей точкой

Сопроцессоры. Что это такое и какие они бывают?

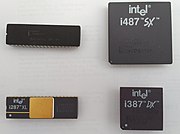

Сопроцессор — специализированный процессор, расширяющий возможности центрального процессора компьютерной системы, но оформленный как отдельный функциональный модуль. Физически сопроцессор может быть отдельной микросхемой или может быть встроен в центральный процессор (как это делается в случае математического сопроцессора в процессорах для ПК начиная с Intel 486DX).

Различают следующие виды сопроцессоров:

Сопроцессоры могут входить в набор логики, разработанный одной конкретной фирмой (например, Intel выпускала для процессоров 8086 и 8088 сопроцессоры 8087 и 8089, Motorola — сопроцессор Motorola 68881) или выпускаться сторонним производителем (например, Weitek (англ.) 1064 для Motorolam68k и 1067 для Intel 80286).

Сопроцессор в программировании

Сопроцессор расширяет систему инструкций центрального процессора, поэтому для его использования программа (компилируемая без интерпретации и вызова внешних библиотек) должна содержать эти инструкции. Настройки современных компиляторов для языков высокого уровня под процессоры семейства x86 зачастую позволяют выбирать: использовать математический сопроцессор или нет, что особенно важно при создании кода, который будет исполняться внутри обработчика аппаратного прерывания.

Также бывают периферийные процессоры, предназначенные для управления периферийными устройствами и разгрузки центрального процессора, а именно:

Звуковые процессоры [Микросхемы звукогенераторов]

Микросхемы звукогенераторов — специализированные микросхемы для генерации звука. Они могут использоваться для воспроизведения звуковых эффектов и синтезированной музыки (см. chiptune) в компьютерах, игровых системах (консолях, автоматах) и бытовой технике. Англоязычное название для микросхем этого типа — sound chip, в русской технической терминологии существует сокращение ПГЗ — программируемый генератор звука. Они могут быть полностью цифровыми, полностью аналоговыми, или смешанного типа. В их состав могут входить генераторы частоты (обычно основанные на делении входной тактовой частоты с программно изменяемым коэффициентом деления), контроллеры огибающей, схемы воспроизведения семплов, фильтры, и усилители сигнала.

Звукогенераторы можно разделить на две основные категории — непосредственно синтезирующие звук, и воспроизводящие заранее оцифрованные звуки. Первая категория также может быть разделена по принципу работы на простые синтезаторы частот (построенные на делителях частоты с дополнительными компонентами), и синтезаторы, использующие метод частотной модуляции (FM-синтез, основан на взаимной модуляции нескольких генераторов звука).

В русском языке микросхемы звукогенераторов нередко называют звуковыми (со)процессорами. Однако, это определение некорректно — микросхемы звукогенератора не занимаются обработкой звуковых данных (основная функция процессора), они генерируют звук по одному определённому аппаратно алгоритму, согласно указаниям внешнего по отношению к ним процессора системы. Название звуковой процессор может применяться к цифровым сигнальным процессорам, используемым для обработки звука (например, создания эффекта программно управляемого эхо), а также к микросхемам звукогенераторов, содержащих в своём составе микропроцессор.

Графический процессор

Графический процессор (англ. graphics processing unit, GPU) — отдельное устройство персонального компьютера или игровой приставки, выполняющее графический рендеринг; в начале 2000-х годов графические процессоры стали массово применяться и в других устройствах: планшетные компьютеры, встраиваемые системы, цифровые телевизоры.

Современные графические процессоры очень эффективно обрабатывают и отображают компьютерную графику, благодаря специализированной конвейерной архитектуре они намного эффективнее в обработке графической информации, чем типичный центральный процессор.

Графический процессор в современных видеокартах (видеоадаптерах) применяется в качестве ускорителя трёхмерной графики.

Может применяться как в составе дискретной видеокарты, так и в интегрированных решениях(встроенных в северный мост либо в гибридный процессор).

Вероятностный процессор

Вероятностный процессор оперирует вероятностями на аппаратном уровне. Математический аппарат основан на теореме Байеса. В некотором роде, вероятностный процессор реализует аналоговые вычисления на технологии КМОП. Подобный подход, теоретически, позволяет эффективно реализовать приближенные вычисления, основанные на нечеткой логике или нейронных сетях.

Области применения

Вероятностный процессор относится к специализированным процессорам и, преимущественно, будет использоваться в системах распознавания образов. Например, в биометрии, для диагностики заболеваний, в различных системах мониторинга, в системах технического зрения, системах распознавания голоса, фильтрации спама, фишинга, определении кредитоспособности заемщиков и многих других задачах. Вероятностный подход также предполагает решение технических задач стохастическими методами (методами Монте-Карло), с любой требуемой точностью решения.

Предполагается, что вероятностный процессор может использоваться в современных компьютерах в качестве еще одного сопроцессора наряду с графическим процессором, сигнальным процессором или ПЛИС (FPGA), обеспечивая высокую скорость и эффективность решения широкого круга специализированных задач.

Прототипы

PCMOS: На Международной конференции по полупроводниковым схемам (ISSCC 2009) исследователи из Rice University показали реально работающий вероятностный процессор PCMOS (англ.) (probability-based complementary metal-oxide semiconductor). Прототип в 7 раз быстрее КМОП (CMOS) чипов, и при этом потребляет в 30 раз меньше энергии.

GP5: Компания Lyric Semiconductor представила прототип специализированного процессора для коррекции ошибок твердотельной (флэш) памяти LEC (Lyric error correction). К 2013 году компания планирует представить универсальный программируемый вероятностный процессор GP5. Для новой аппаратной архитектуры разрабатывается новый язык программирования PSBL (Probability Synthesis to Bayesian Logic). Представить первую версию PSBL планируется в конце 2010 г.

Математический сопроцессор

Математический сопроцессор — сопроцессор для расширения командного множества центрального процессора и обеспечивающий его функциональностью модуля операций с плавающей запятой, для процессоров, не имеющих интегрированного модуля.

Модуль операций с плавающей запятой (или с плавающей точкой; англ. floating point unit (FPU)) — часть процессора для выполнения широкого спектра математических операций над вещественными числами.

Простым «целочисленным» процессорам для работы с вещественными числами и математическими операциями требуются соответствующие процедуры поддержки и время для их выполнения. Модуль операций с плавающей запятой поддерживает работу с ними на уровне примитивов — загрузка, выгрузка вещественного числа (в/из специализированных регистров) или математическая операция над ними выполняется одной командой, за счёт этого достигается значительное ускорение таких операций.

x87 — это специальный набор инструкций для работы с математическими вычислениями, являющийся подмножеством архитектуры процессоров x86. Такое название он получил, потому что первоначальные отдельные математические сопроцессорные чипы имели названия, заканчивающиеся на 87. Как и другие расширения базового набора инструкций процессора, эти инструкции не являются строго необходимыми для построения рабочей программы, но будучи аппаратно реализованными, общие математические задачи они позволяют выполнять гораздо быстрее. Например, в наборе инструкций x87 присутствуют команды для расчёта значений синуса или косинуса.

Сопроцессоры Intel семейства x86

Для процессоров семейства x86 с 8086/8088 по 386 модуль операций с плавающей запятой был выделен в отдельную микросхему, называемую математическим сопроцессором. Для установки сопроцессора на плате компьютера предусматривался отдельный разъём.

Сопроцессор не является полноценным процессором, так как не умеет делать многих необходимых для этого операций (например, не умеет работать с программой и вычислять адреса памяти), являясь всего лишь придатком центрального процессора.

Одна из схем взаимодействия центрального процессора и сопроцессора, применяемая, в частности, в x86-сопроцессорах, реализуется следующим образом:

Начиная с процессора Intel486DX модуль операций с плавающей запятой был интегрирован в центральный процессор и назван FPU. В линейке Intel486SXмодуль FPU отключался (поначалу в эту линейку попадали процессоры с бракованным FPU). Для процессоров Intel486SX также выпускался «сопроцессор» Intel487SX, но фактически он являлся процессором Intel486DX, и при его установке процессор Intel486SX отключался.

Несмотря на интеграцию, FPU в процессорах i486 представляет собой неизменный сопроцессор, выполненный на том же кристалле, более того, схема FPU i486 полностью идентична сопроцессору предыдущего поколения 387DX вплоть до тактовой частоты (в два раза меньшей, чем частота центрального процессора). Настоящая интеграция FPU c центральным процессором началась только в процессорах Pentium модели MMX.

Сопроцессоры x86 от сторонних производителей

Широкое распространение в соответствующий период получили сопроцессоры для платформы x86, выпускавшиеся компанией Weitek — ею были выпущены 1167, 2167 в виде набора микросхем и микросхемы 3167, 4167, для процессоров 8086, 80286, 80386, 80486, соответственно. По сравнению с сопроцессорами от Intel они обеспечивали в 2—3 раза большую производительность, но обладали несовместимым программным интерфейсом, реализованным через технологию memory-mapping. Она сводилась к тому, что основной процессор должен был записывать информацию в те или иные области памяти, контролируемые Weitek-овским сопроцессором (собственной оперативной памяти там не было). Конкретный адрес, куда производилась запись, интерпретировался в качестве той или иной команды. Несмотря на несовместимость, сопроцессоры от Weitek были широко поддержаны как разработчиками ПО, так и производителями материнских плат, предусматривавших на них гнёзда для установки такой микросхемы.

Ряд других компаний также выпускал различные несовместимые математические сопроцессоры, реализуя интерфейс к ним через порты ввода-вывода или прерывания BIOS, но они не получили такого широкого распространения.

Компании-производители клонов выпускали совместимые с 80287 80387 сопроцессоры, работавшие быстрее аналогичных интеловских. Среди этих компаний можно упомянуть Cyrix, AMD, Chips & Technologies (C&T). Иногда система команд этих сопроцессоров расширялась несколькими несовместимыми, например, аналог 80287 от C&T содержал команды для работы с вектором из четырёх значений с плавающей точкой. Серьёзной поддержки от производителей ПО эти расширенные команды не получили.

Процессоры EMC87 от фирмы Cyrix могли работать как в режиме программной совместимости с Intel 80387, так и в собственном несовместимом режиме программирования. Для них обеспечивалась аппаратная совместимость с разъёмом 80387-го сопроцессора.

В СССР выпускалась микросхема (КМ)1810ВМ87, которая являлась аналогом 8087.

Другие платформы

Аналогично, материнские платы ПК, построенных на процессорах Motorola, до разработки этой фирмой процессора MC68040 (в который сопроцессор был встроен) содержали математический сопроцессор. Как правило, в качестве FPU использовался сопроцессор 68881 16 МГц или 68882 25 МГц. Практически любой современный процессор имеет встроенный сопроцессор. Компания Weitek также выпускала математические сопроцессоры для платформ 68000 и MIPS.

Устройство FPU

Все процессоры Intel и AMD, начиная с 486DX, имеют встроенный математический сопроцессор, и в отдельном сопроцессоре не нуждаются (за исключением Intel486SX). Тем не менее, термин x87 всё ещё используется для выделения той части инструкций процессора, которая занимается вычислениями с использованием плавающей запятой; компиляторы могут использовать эти инструкции для производства кода, который работает быстрее, нежели тот, что использует вызовы к библиотекам для выполнения операций с плавающей запятой.

Инструкции x87 совместимы со стандартом IEEE-754. Однако x87 выполняют операции не в строгом соответствии с форматами IEEE-754, из-за использования более широких регистров. Поэтому последовательность арифметических операций может выполняться несколько по-разному на наборе x87и на процессоре, строго следующем формату IEEE-754.

x87 организует свои регистры не как массив, как большинство других архитектур, а как регистровый стек, работающий по принципу обратной польской записи. Это означает, что в один момент времени только два верхних регистра доступны для проведения операций, а доступ к другим регистрам требует манипуляций со стеком. Хотя такая организация получается и удобной для программистов, она делает трудоёмким построение эффективного кода x87 для компиляторов.

Начиная с Pentium III, вычисления с помощью инструкций SSE осуществляются с одинарной точностью, а в более поздних версиях — с двойной точностью форматов IEEE-754. После появления SSE2 использование x87 в значительной степени умалчивается в 64-разрядных архитектурах x86-64 и связанных с ней 64-битных реализациях операционных систем, таких, как Microsoft Windows, Mac OS X, Solaris, FreeBSD и Linux, хотя он по-прежнему хорошо поддерживается для полной совместимости со старыми приложениями.

Модуль операций с плавающей запятой представляет собой стековый калькулятор, работающий по принципу обратной польской записи. Перед операцией аргументы помещаются в LIFO-стек, при выполнении операции необходимое количество аргументов снимается со стека. Результат операции помещается в стек, где может быть использован в дальнейших вычислениях или может быть снят со стека для записи в память. Также поддерживается и прямая адресация аргументов в стеке относительно вершины.

Форматы данных

Внутри FPU числа хранятся в 80-битном формате с плавающей запятой, для записи же или чтения из памяти могут использоваться:

FPU также поддерживает специальные численные значения:

Регистры

В FPU можно выделить три группы регистров:

Система команд сопроцессора

Система включает около 80 команд. Их классификация:

Super I/O

Super I/O (англ. Super Input/output; дословно: супер ввода-вывода) — название класса сопроцессоров, которые начали использоваться после 1980-х годов на материнских платах IBM PC-совместимых компьютеров путём сочетания функций многих контроллеров, сперва одной платой, устанавливаемой в слот расширения, а затем и одной микросхемой, тем самым достигая уменьшения числа микросхем контроллеров, и таким образом привели к снижению сложности и стоимости компьютера в целом. Super I/O объединяет интерфейсы различных низкоскоростных устройств.

Фактически, на рынке материнских плат массового сегмента предоставлена продукция всего четырёх фирм: ITE Tech, Nuvoton, Microchip Technology и Fintek. Производители брендовой продукции (IBM, HP, Dell, FSC) как правило используют проприетарные разработки схемотехники материнских плат и не публикуют спецификаций применяемых контроллеров.

Как правило, включает в себя следующие функции:

Super I/O также может включать в себя и другие интерфейсы, такие как игровой (MIDI или джойстик) или инфракрасный порты.

Изначально Super I/O связывались через шину ISA. Одновременно с развитием IBM PC-совместимых компьютеров происходило смещение Super I/O, сперва на шины VLB, затем стала использоваться шина PCI. Современные Super I/O используют шину LPC (интерфейс которой предоставляет южный мост материнской платы) и часто реализованы в составе чипсета.

В компьютерных архитектурах общего назначения один или несколько блоков FPU могут быть интегрированы в качестве исполнительных блоков в центральный процессор ; однако многие встроенные процессоры не имеют аппаратной поддержки операций с плавающей запятой (хотя они все чаще имеют их в стандартной комплектации, по крайней мере, 32-разрядные).

Когда ЦП выполняет программу, которая вызывает операцию с плавающей запятой, есть три способа выполнить ее:

СОДЕРЖАНИЕ

История

В 1963 году GE-235 был оснащен «вспомогательным арифметическим устройством» для вычислений с плавающей запятой и двойной точности.

Библиотека с плавающей точкой

| В Wikibooks есть книга на тему: Плавающие точки / Программные реализации. |

| В Викиучебнике есть книга по теме: Встроенные системы / Блоки с плавающей запятой. |

Интегрированные FPU

В некоторых современных архитектурах функциональность FPU объединена с модулями SIMD для выполнения вычислений SIMD; Примером этого является расширение набора инструкций x87 с помощью набора инструкций SSE в архитектуре x86-64, используемой в новых процессорах Intel и AMD.

Дополнительные FPU

В 1980-х годах в IBM PC / совместимых микрокомпьютерах было обычным делом, чтобы FPU был полностью отделен от процессора и обычно продавался как дополнительное дополнение. Его можно будет купить только в том случае, если это необходимо для ускорения или включения математических программ.

Почти все, что вы хотели знать про плавающую точку в ARM, но боялись спросить

Флаги компилятора

‘auto’, ‘vfpv2’, ‘vfpv3’, ‘vfpv3-fp16’, ‘vfpv3-d16’, ‘vfpv3-d16-fp16’, ‘vfpv3xd’, ‘vfpv3xd-fp16’, ‘neon-vfpv3’, ‘neon-fp16’, ‘vfpv4’, ‘vfpv4-d16’, ‘fpv4-sp-d16’, ‘neon-vfpv4’, ‘fpv5-d16’, ‘fpv5-sp-d16’, ‘fp-armv8’, ‘neon-fp-armv8’ and ‘crypto-neon-fp-armv8’. Причем ‘neon’ это тоже самое что и ‘neon-vfpv3’, а ‘vfp’ это ‘vfpv2’.

Мой компилятор (arm-none-eabi-gcc (15:5.4.1+svn241155-1) 5.4.1 20160919) выдаёт немного другой список, но сути дела это не меняет. Нам в любом случае нужно понять, как влияет тот или иной флаг на работу компилятора, ну и конечно, какой флаг когда следует использовать.

Для того чтобы, разрешить работу сопроцессора нужно установить бит EN [30] в регистре FPEXC. Делается это с помощью команды VMSR

Вообще-то команда VMSR обрабатывается сопроцессором и вызывает исключение, если не включен сопроцессор, но обращение к этому регистру его не вызывает. Правда, в отличие от остальных, обращение к этому регистру возможно только в привилегированном режиме.

После разрешения работы сопроцессора стали проходить наши тесты на математические функции. Но когда я включил оптимизацию (-O2), стало возникать уже упомянутое ранее исключение undefined instruction. Причем возникало оно на инструкции vmov которая вызывалась в коде раньше, но исполнялась успешно (без возникновения исключения). Наконец, я обнаружил в конце приведенной страницы фразу “The instructions that copy immediate constants are available in VFPv3” (т.е. операции с константами поддерживаются начиная с VFPv3). И решил проверить, какая же версия релизована в моем эмуляторе. Версия записана в регистре FPSID. Из документации следует, что значение регистра должно быть 0x41011090. Это соответствует 1 в поле architecture [19..16] то есть VFPv2. Собственно, сделав распечатку при старте, я это и получил

Ассемблер

Пришло время поговорить об ассемблере. Ведь мне нужно было сделать и поддержку рантайма, а, например, про переключение контекста компилятор, конечно, не знает.

Регистры

Начнем с описание регистров. VFP позволяет совершать операции с 32-битными (s0..s31) и 64-битными (d0..d15) числами с плавающей точкой, Соответствие между этими регистрами показано на картинке ниже.

Q0-Q15 — это 128-битные регистры из более старших версий для работы с SIMD, о них чуть позже.

Система команд

Конечно, чаще всего работу с VFP-регистрами стоит отдать компилятору, но как минимум переключение контекста придётся написать вручную. Если у вас уже есть примерное понимание синтаксиса команд ассемблера для работы с регистрами общего назначения, разобраться с новыми командами не должно составить большого труда. Чаще всего просто добавляется приставка “v”.

И так далее. Полный список команд можно посмотреть на сайте ARM.

Ну и конечно не стоит забывать о версии VFP, чтобы не возникло ситуаций вроде той, что описана выше.

‘softfp’ allows the generation of code using hardware floating-point instructions, but still uses the soft-float calling conventions. ‘hard’ allows generation of floating-point instructions and uses FPU-specific calling conventions.

“Compiler can make smart choices about when and if it generates emulated or real FPU instructions depending on chosen FPU type (-mfpu=) “

На вопрос, какой же флаг использовать ‘softfp’ или ‘hard’, я ответил для себя следующим образом: везде где нет уже скомпилированных с флагом ‘softfp’ частей, следует использовать ‘hard’. Если же такие есть, то необходимо использовать ‘softfp’.

Переключение контекста

Поскольку Embox поддерживает вытесняющую многозадачность, для корректной работы в рантайме, естественно, нужна была реализация переключения контекста. Для этого необходимо сохранять регистры сопроцессора. Тут есть пара нюансов. Первый: оказалось что команды операций со стеком для плавающих точек (vstm/vldm) поддерживают не все режимы. Второй: эти операции не поддерживают работу более, чем с шестнадцатью 64-битных регистров. Если за раз нужно загрузить/сохранить больше регистров, нужно использовать две инструкции.

Еще приведу одну небольшую оптимизацию. На самом деле, каждый раз сохранять и восстанавливать по 256 байт VFP-регистров совсем не обязательно (регистры общего назначения занимают всего 64 байта, так что разница существенная). Очевидной оптимизацией будет совершать эти операции только если процесс этими регистрами в принципе пользуется.

Как я уже упоминал, при выключенном сопроцессоре VFP попытка исполнить соответствующую инструкцию будет приводить к исключению “Undefined Instruction”. В обработчике этого исключения нужно проверить, чем исключение вызвано, и если дело в использовании VPF-сопроцессора, то процесс помечается как использующий VFP-сопроцессор.

В итоге уже написанное сохранение/восстановление контекста дополнилось макросами

Для проверки корректности работы переключения контекста в условиях работы с плавающей точки мы написали тест, в котором в одном потоке в цикле мы делаем умножение, а в другом деление, потом сравниваем результаты.

Сопроцессор NEON и SIMD

Пришло время рассказать, почему я отложил рассказ про imx6. Дело в том что он основан на ядре Cortex-A9 и содержит более продвинутый сопроцессор NEON (https://developer.arm.com/technologies/neon ). NEON не только является VFPv3, но это еще и сопроцессор SIMD. VFP и NEON используют одни и те же регистры. VFP использует для работы 32- и 64-разрядные регистры, а NEON — 64- и 128-битные, последние как раз и были обозначены Q0-Q16. Помимо целых значений и чисел с плавающей точкой NEON также умеет работать с кольцом многочленов 16-й или 8-й степени по модулю 2.

но других принципиальных отличий нет.

Использование SIMD в C

Для того, чтобы > значения по регистрам вручную, можно заинклудить “arm_neon.h” и использовать соответствующие типы данных:

float32x4_t для четырёх 32-битных флоатов в одном регистре, uint8x8_t для восьми 8-битных целых чисел и так далее. Для обращения к одному значению обращаемся как к массиву, сложение, умножение, присвоение и т.д. как для обычных переменных, например:

Цикл со сложениями генерирует следующий код:

Проведя тесты на распараллеленный код, получили, что простое сложение в цикле, при условии независимости переменных дает ускорение аж в 7 раз. Кроме того, мы решили посмотреть, насколько влияет распараллеливание на реальных задачах, взяли MESA3d с его программной эмуляцией и померили количество fps с разными флагами, получился выигрыш в 2 кадра в секунду (15 против 13), то есть, ускорение около 15-20%.

Приведу еще один пример ускорения с помощью команд NEON, не нашего, а от ARM-а.

Копирование памяти ускоряется почти на 50 процентов по сравнению с обычным. Правда примеры там на ассемблере.

Обычный цикл копирования:

цикл с командами и регистрами neon:

Понятно, что копировать по 64 байта быстрее чем по 4 и такое копирование даст прирост на 10%, но остальные 40% похоже дает работа сопроцессора.

Cortex-M

Работа с FPU в Cortex-M мало чем отличается от описанного выше. Например, вот так выглядит приведенный выше макрос для сохранения fpu-шного контекста

Основным же отличием является доступ к управляющим регистрам контроллера они расположены прямо в адресном пространстве основного ядра для причем для разных типов они разные cortex-m4 для cortex-m7.